Dalam Perencanaan suatu sistem rangkaian elektronik, langkah teknik yang dilakukan pertama kali adalah menggambarkan seluruh sistem dengan blok diagram. Dengan blok diagram ini, dapat diketahui bagaimana prinsip kerja umum dan hubungan antara subblok satu dengan yang lain dalam membentuk sistem kerja yang utuh.

Merencanakan suatu peralatan kontrol elektronik yang berbasis mikroprosesor memerlukan pemahaman yang cukup tentang aspek-aspek sistem yang optimal. Orientasi desain dapat dicapai dengan dua cara yaitu orientasi subyek dan orientasi obyek. Orientasi subyek berasal dari peranti kontrol yang telah ada sebelumnya. User hanya tinggal merancang sistem interface dari peranti kontrol. Sedangkan orientasi obyek adalah berasal dari obyek yang akan dikontrol. Penerjemahan peranti kontrol, atau bentuk rangkaian kontrol seperti apa yang dikehendaki, dibangun dengan pendekatan fungsi dalam pengontrolan yang telah didefinisikan.

Membangun dari awal suatu sistem rangkaian berbasis mikroprosesor sebagai sistem kontrol elektronik dapat dikategorikan sebagai langkah desain dengan menggunakan berorientasi pada obyek. Dari fenomena inilah muncul pengertian sistem minimum, yang dapat diterjemahkan sebagai sistem rangkaian yang minim dan dapat digunakan sebagai rangkaian kontrol dalam menjawab permasalahan obyek yang harus disesaikan.

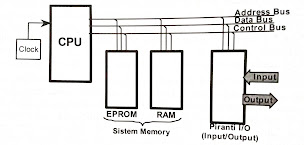

blok

sistem rangkaian berbeasis mikroprosesor Z80 dalam bentuk yang paling ringkas, tetapi telah memenuhi sebagai sistem kontrol elektronik yang ditunjukkan dalam diagram pada gambar diatas. sistem tersebut terdiri dari 3 komponen pendukung utama yaitu:

1. CPU/Mikroprosesor

2. Sistem Memory (dapat berupa EPROM dan RAM)

3. Sistem Peranti I/O (Input/Output) berupa IC pheriperal.

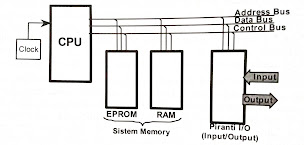

Sedangkan yang disebut sebagai sistem yang dikontrol diilustrasikan seperti gambar berikut.

blok diagram tersebut mewakili seluruh model permasalahan yang dapat diatur dengan kontrol elektronik.

gambar tersebut adalah gambar apabila sistem rangkaian pengontrol digabung dengan rangkaian yang dikontrol, maka blok diagramnya menjadi seperti gambar tersebut.

LINGKUP PERANCANGAN SISTEM MINIMUM CPU Z80

CPU Z80 memiliki 8-bit data dan 16-bit alamat. Ia dapat dirangkai dengan hampir semua komponen memory standar yang tersedia di pasaran. Kemampuan pengalamatan memory maksimum secara langsung adalah sebesar (64 Kilo x 8 bit) atau sebesar 64 KiloByte, dapat diterangkan dengan pemetaan memory seperti gambar dibawah. Pengalamatan untuk CPU 8-bit umumnya memiliki 16-bit alamat sama seperti Z80.

Pada dasarnya , pemanfaatan lokasi memory sebanyak ini dapat dicapai dengan menggunakan RAM saja, EPROM saja atau keduanya dengan peraturan peta memory tertentu. Tetapi kenyataannya, suatu permasalahan teknik kontrol yang diselesaikan dengan rangkaian elektronik berbasis mikroprosesor selalu menggunakan EPROM maupun RAM dalam satu rangkaian.

RANGKAIAN CLOCK

Syarat utama agar CPU dapat bekerja adalah dengan tersedianya rangkaian clock yang memadai. Frekuensi kerja clock tidak boleh melebihi kemampuan maksimal frekuensi kerja CPU.

Gambar diatas adalah contoh rangkaian clock yang dapat digunakan dalam sistem rangkaian minimum Z80. Rangkaian ini dipakai dalam rangkaian mikrokomputer FZ80.Untuk sistem rangkaian CPU Z80, selain menggunakan rangkaian clock seperti gambar diatas, terdapat juga rangkaian clockyang telah terintegrasi.

CPU BUS BUFFER (RANGKAIAN PENYANGGA BUS CPU)

Bila CPU dihubungkan ke berbagai macam pheriperal dengan jumlah yabg relatif banyak, bus bus CPU akan bekerja cukup berat. Ia harus dapat menyokong data atau logika ke memory atau pheriperal dengan tegangan yang memenuhi syarat. Maksudnya, meskipun bus bus CPU terhubung ke berbagai macam komponen memory atau pheriperal , CPU harus tetap dapat memberikan logika yang valid.

berikut ini adalah ilustrasi pemasangan rangkaian buffer pada CPU.

Untuk sistem rangkaian berbasis mikroprosesor yang berorientasi pada CMOS, rangkaian buffer ini jarang sekali digunakan karena IC CMOS memiliki keistimewaan pada arus kemudi input yang sangat kecil sekitar 2-10 miu ampere untuk tiap gate dan arus output gate sampai 5mA sehingga fungsi fan out menjadi jaugh lebih besar dibanding tipe TTL. Namun apabila menggunakan CPU tipe Z80 atau Z80A (bukan tipe CMOS) maka dianjurkan untuk menggunakan rangkaian buffer untuk meningkatkan fungsi fan-in dan fan-outnya.

RANGKAIAN AUTO RESET POWER ON

Dalam sistem rangkaian berbasis mikroprosesor yang diaplikasikan sebagai alat kontrol, sering dibutuhkan suatu kondisi yang mensyaratkan rangkaian untuk dapat langsung bekerja (running) begitu tegangan Vee diberikan. Dalam hal ini, rangkaian CPU Z80 perlu diberi waktu beberapa mikrodetik sebelum instruksi di alamat 0000H mulai dilaksanakan, untuk memastikan bahwa semua bagian rangkaian sudah mencapai 'steady state' atau kondisi stabil saat CPU mulai bekerja.

Untuk memenuhi kebutuhan ini perlu digunakan suatu rangkaian yang disebut sebagai 'Auto Reset Power ON. Begitu switch Power di-ON-kan, pin RESET dibuat aktif sampai beberapa mikrodetik, tergantung nilai parameter- parameter rangkaian delay (penunda). Kemudian secara otomatis RESET menjadi nonaktif. Penentuan nilai parameter delay (R dan C) tergantung pada tipe-tipe IC keseluruhan yang digunakan dalam rangkaian. Terutama bagi IC Peripheral yang memiliki fungsi RESET. Seluruh peripheral pendukung harus dalam keadaan yang stabil pada saat CPU mulai bekerja mengeksekusi instruksi pertama.

Perlu diingat bahwa tidak semua peripheral yang dapat dirangkai dengan CPU Z80 memiliki kompatibilitas penuh dengan 280 ini, terutama dalam hal pewaktuan (timing).

Gambar tersebut merupakan contoh rangkaian auto reset power on untuk CPU Z80 yang dilengkapi dengan push button untuk manual reset. untuk model rangkaian reset yang paling ringkas dapat digunakan rangkaian push button seperti gambar diabwah ini.

INTERFACING Z80 KE IC MEMORY

Di muka, telah diterangkan bahwa EPROM yang populer dan memungkin-kan untuk digunakan dalam sistem minimum 280 adalah tipe 2708, 2716, 2732, 2764, 27128 dan 27256, baik dalam kelas CMOS maupun non-CMOS. Tipe EPROM di atas 27256, misalnya 27512 dan 27C1001, tidak sesuai untuk digunakan pada sistem berbasis Z80 karena kapasitas memorinya di atas 64KB. Untuk tipe antara lain adalah 6116, 6264 dan 62256. Dalam memilih IC memory ini, dianjurkan untuk mem-per-timbangkan kemungkinan penggunaan memori dari program yang mungkin diaplikasikan dalam sistem, di mana program ini disimpan di EPROM, dan mempertimbangkan pula peng- gunaan struktur stack dan area data yang bisa terjadi (direncanakan untuk dihasilkan) selama program yang berada di dalam EPROM dijalankan (running).

Jadi, pemilihan suatu EPROM atau RAM tidak didasarkan hanya pada bagaimana membuat sistem rangkaian memon selengkap mungkin, tetapi juga berapa besar memori yang sebenarnya kita butuhkan untuk menyelesai- kan permasalahan kontrol elektronik itu. Dalam perancangan atau pemilihan alamat kerja masing-masing IC memory, perlu juga dipertimbang-kan dengan teliti cara

pemisahan alamat-alamat kerja untuk penggunaan lebih dari sebuah EPROM dengan tipe yang sama. Bagaimana merancang rangkaian pemisah atau rangkaian dekoder menggunakan IC dekoder yang seefisien mungkin, atau bahkan tanpa menggunakan bantuan IC dekoder, melainkan cukup memanfaatkan jalur-jalur alamat yang ada pada address bus. Uraian-uraian berikut ini akan menerangkannya.

Pertama, perhatikan pemetaan memori dari masing-masing EPROM: 2708, 2716, 2732, 2764, 27128 dan 27256 pada Gambar 5.9, kemudian RAM: 6116, 6264 dan 62256. Masing-masing peta memori digambarkan mulai alamat 0000H untuk menunjukkan bahwa kapasitas memori yang dimiliki setara dengan jangkauan pengalamatan yang mungkin dilakukan.

EPROM 2708 memiliki jalur alamat sebanyak 10 buah yang terdiri dari A9 sampai A0. Kapasitas memorinya adalah 8 Kilo bit (Kb) atau 1 Kilo Byte (KB). Dalam hubungan rangkaian ke sistem minimum, A9 sampai A0 ini dapat dihubungkan langsung ke A9 sampai A0 pada address bus Z80, sedangkan A15 sampai A10 dari address bus digunakan untuk membentuk address decoding dari EPROM guna menentukan daerah alamat tempat EPROM ini akan dioperasikan.

EPROM 2716 memiliki kapasitas dua kali lebih besar dari 2708, yaitu16 Kb atau 2 KB, memiliki jalur alamat A10 sampai A0. Ini menunjukkanbahwa penambahan satu jalur di posisi MSB, yaitu A10, akan menambahkapasitas muatan memorinya hingga dua kali lipat.

EPROM 2732 memiliki kapasitas 32 Kb atau 4KB, dua kali lipat dari 2716, karena jalur alamatnya All hingga AO EPROM 2764 memunyai kapasitas 64 Kb atau 8 KB, dua kali lipat dari 2732, karena jalur alamatnya terdiri dari A12 hingga AO. EPROM 27128 memiliki kemampuan 128 Kb atau 16 KB karena jalur alamatnya A13 hingga A0. Terakhir, EPROM 27256, memunyai kapasitas memori 256 Kb atau 32 KB karena jalur alamatnya adalah A14 hingga A0,

Semakin besar kapasitas memorinya, semakin banyak pula jalur alamatnya, dan secara relatif semakin mudah pula perancangan rangkaian pemisah alamat atau rangkaian dekoder yang dibutuhkan. Bila kita gunakan EPROM 27256 dan RAM 62256 maka kita tidak perlu memasang rangkaian dekoder khusus (misalnya IC dekoder 74HC138) untuk memisahkan alamat kerja kedua IC memory tersebut. Cukup dengan memanfaatkan A15 pada CPU 280, dihubungkan ke cs (Chip Select) masing-masing IC memory dengan cara tertentu sehingga kedua IC tersebut akan bekerja pada alamat- alamat yang terpisah. 32KB yang pertama (dari alamat 0000H sampai 7FFFH) digunakan oleh EPROM 27256, sedangkan 32KB yang kedua (alamat dari 8000H sampai FFFFH) digunakan oleh RAM 62256.

MANIPULASI KONTROL READ/WRITE UNTUK MEMORY DAN PERANTI I/O

Pada EPROM, selam memilik cs (Chip Select), ia juga memiliki jalur kontrol of (Output Enable) yang aktif pada logika '0' juga or im juga harus diaktifkan oleh CPU agar data EPROM dapat dibaca. Adapun pada RAM, selain terdapat CS (atau CE) dan OF, juga terdapat we (Write Enable), yang berguna untuk kontrol penulisan data ke RAM

Proses pembacaan data yang dilakukan oleh CPU Z80 tidak saja berlaku bagi memori, tetapi juga bagi peralatan Input Port Berdasarkan diagram pewaktuan (timing) read/write memory dan 1/O read/write dapat dilihat bahwa pengaktifan instruksi yang menyebabkan CPU menghubungi memori (EPROM maupun RAM) akan mengaktifkan MREQ, dan RD atau WR, sedangkan 10RQ (Input/Output Request) tidak aktif. Sebaliknya, untuk proses membaca data yang berasal dari Input Port, dengan mengeksekusi instruksi IN [misalnya: in a,(81h)], maka yang aktif adalah 1ORO dan RD, tetapi MREQ tidak demikian.

Perbedaan aktif dan nonaktif dari MREQ dan IORQ inilah yang dijadi- kan acuan tindak lanjut pembuatan rangkaian penghasil sinyal aktif yang spesial untuk memori atau spesial untuk rangkaian Input Port. Lihat Gambar 5.11. MREQ di-OR-kan dengan RD menjadi MEMRD (Memory Read) dan dapat digunakan untuk menghubungi RAM ataupun ROM MREQ digabung dengan WR melalui operasi OR menghasilkan sinyal aktif MEMWR (Memory Write) dan digunakan khusus untuk menulis data ke RAM. Untuk VO, JORO di-OR-kan dengan RD menjadi 1ORD (Input Read) dan berfungsi untuk mengaktifkan pembacaan data dari Input Port, sedangkan bila di- gabung dengan WR, sinyal aktif yang dihasilkan adalah 10WR (Output Write) yang berguna untuk penulisan data ke Output Port.

INTERFACING CPU Z80 KE PERANTI I/O

Pada dasarnya, menghubungkan bus dari CPU Z80 ke rangkaian Input atau Output Port identik dengan cara menghubungkan CPU ke memori. Perlu diperhatikan bahwa instruksi yang dapat digunakan untuk menghubungi Input/Output Port, yaitu instruksi IN dan OUT, hanya dapat dikenakan pada alamat-alamat dari 0000H sampai 00FFH atau 00H sampai FFH atau hanya pada alamat 8-bit yang Low-Order.

Jika dinyatakan dalam lebar jalur alamat maka hanya perlu mem- perhatikan A7 sampai A0 untuk konfigurasi logika yang mungkin '0' atau '1'. Adapun A15 sampai A8 harus selalu '0'. Hal ini berpengaruh langsung ter- hadap bentuk rangkaian dekoder yang dibutuhkan untuk memisahkan alamat kerja Input/Output Port. A15 sampai A8 dapat langsung diabaikan, tanpa menghubungkannya ke rangkaian I/O Port, dan cukup memperhatikan A7 sampai A0.

Membangun peranti Input/Output dengan menggunakan seluruh IC TTL akan jumlah komponen yang relatif banyak. Dalam aplikasi banyak hal, perancang lebih suka menggunakan IC khusus yang dapat dihubungkan dengan berbagai CPU sebagai Parallel Input/Output Port. Salah satunya adalah Programmable Peripheral Interface (PPI) 8255. Selain itu juga terdapat Z80PIO yang khusus dalam lingkung perancangan sistem berbasis CPU Z80.

PROGRAMABLE PERIPHERAL INTERFACE (PPI) 8255

PPI 8255 adalah suatu peranti paralel input/output dalam satu chip serbaguna yang fungsi input/outputnya dapat diprogram. Awalnya, PPI 8255 dibuat oleh Intel untuk digunakan bersama dengan mikroprosesor buatan Intel. Namun, karena komponen ini berbasis standard bus dan tata cara perangkaiannya relatif mudah maka kebanyakan tipe mikroprosesor lain juga dapat me-manfaatkannya.

PPI 8255 memunyai 24 pin I/O yang terdiri dari 3 port, yaitu Port A (8 pin), Port B (8 pin) dan Port C (8 pin). Port A dan Port C pada PC7 sampai PC4 tergabung dalam Grup Kontrol A, sedangkan Port B dan Port C dari PC3 sampai PCO tergabung dalam Grup Kontrol B. 8255 ini dapat dioperasikan dalam 3 mode, yaitu Mode 0, Model dan Mode 2.

Deskripsi tentang fungsi pin 8255 adalah sebagai berikut:

PA7-PAO : Terminal I/O Port A

PB7-PB0 : Terminal I/O Port B

PC7-PC0 : Terminal I/O Port C.

CS : Chip Select (input, active low)

Bila CS diset '0' maka PPI sedang dihubungi CPU

RD : Read (input, active low).

Bila RD diset '0', artinya CPU sedang membaca data dari 8255.

WR : Write (input, active low).

WR diset '0' menunjukkan bahwa CPU sedang menulis data ke 8255

A0 & AI : Port Select 0 dan Port Select 1 (input).

Kombinasi A0 dan Al digunakan untuk memilih port mana yang bekerja.

+5V & GND : Terminal Tegangan Supply & Ground.

REFERENSI :

Buku Mikroprosesor dan Interfacing (Endra Pitowarno) Penerbit Andi Yogyakarta Tahun 2005

Tidak ada komentar:

Posting Komentar